### **ISIM**

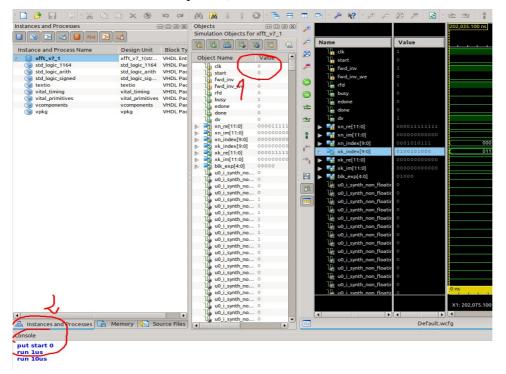

Die Signale können entweder mit Rechtsklick auf den Signalwert (1) oder über die Konsole (2) eingegeben werden.

- (1) force constant bzw. force clock

- (2) put

Praktisch ist es, eine Textdatei für die Simulation zu schreiben und mit Cut&Paste den gesamten Inhalt in die Konsole zu kopieren; die Befehle werden dann der Reihe nach abgearbeitet.

## Das Wichtigste in Kürze

- Groß-/Kleinschreibung beachten! (??? nicht in Linux)

- Die wichtigsten Befehle

- restart

- o put

- o force

- o run

- o add wave (um ein internes Signal zu beobachten)

- New Devider ... bunte Trennlinien einfügen

- New Virtual Bus ... Signale zusammenfassen ; mit "Radix" eine Zahlendarstellung wählen

### Simulations-Skript

Im Editor schreiben und per Cut&Paste in die Konsole kopieren

```

#ISIM Simulation kner 2011 (FFT-Modul)

put start 0

put fwd inv 1

put fwd inv we 0

put xn re 000011111111

put xn im 000000000000

isim force add {/xfft_v7_1/clk} 0 -radix bin -value 1 -radix bin -time 5 ns

-repeat 10 ns

run 50ns

put fwd inv we 1

run 50ns

put fwd_inv_we 0

run 50ns

put start 1

run 50ns

put start 0

run 100us

#warten, bis die Daten verarbeitet sind

put start 1

# nächster Frame; die Ergebnisse stehen am Ausgang an

run 20ns

put start 0

```

#### **Force**

```

isim force add rst 0

isim force add rst 1 -time 10 ns -cancel 50 ns

isim force add clk 1 -value 0 -time 20 ns -repeat 40 ns -cancel 1 us

isim force add data_in 1 -value 0 -time 50 ns -value 1 -time 75 ns -repeat 100

ns -cancel 5000 ns

isim force add in0 0 -value 1 -time 20ns -value 0 -time 40ns -cancel 60ns

isim force remove s s1 s2

```

## Interpretation des Simulator-Outputs – IEEE std\_logic\_1164.vhd

- 'U': uninitialisiert; der Wert wurde noch nicht gesetzt (z.B. Flipflop vor einem Reset)

- 'X': unknown; unmöglich, den Wert zu bestimmen (es kämpft eine starke 1 gegen eine starke 0)

- '0': logische 0; stark

- '1': logische 1;

- 'Z': High Impedance; Unterbrechung, offener Schalter, offener Eingang

- 'W': schwaches X; (schwache 1 kämpft gegen schwache 0)

- 'L': schwache 0

- 'H': schwache 1

- '-': Don't care

## Beispiele

```

signal s1, s2 : std_logic;

...

variable v1, v2 : std_logic;

...

s1 <= '0';

v1 := '1';

s2 <= 'X';

wait for 10 ns;

s2 <= s1 and v1; -- '0'

v2 := s1 or v1; -- '1'</pre>

```

# Eine kleine Übung

Simulieren Sie ein Und-Gatter (Instanz auswählen und und legen Sie an die Eingänge folgende Pegel an:

| Input |    | Ouput |

|-------|----|-------|

| i0    | i1 | 0     |

| 0     | 0  | 0     |

| 1     | 1  | 1     |

| 1     | 0  | 0     |

| X     | L  | 0     |

| Н     | 1  | 1     |

| Z     | 1  | X     |

| X     | 1  | X     |

| W     | 1  | X     |

| U     | 1  | U     |